# MACHINEWARE

## SIM-V

Fast, Parallel RISC-V Simulation for Rapid Software Verification

Lukas Jünger, MachineWare GmbH Jan Henrik Weinstock, MachineWare GmbH Rainer Leupers, RWTH Aachen University

As presented at DVCON Europe 2022

### Virtual Prototyping

- Virtual Platform: Full System Simulation

- Indispensable in software development

- Everising SW and HW complexity

- Advantages over physical prototypes

- Available earlier (shift-left methodology)

- Full flexibility, deep introspection

- Non-intrusive debug

- More scalable (e.g. in the cloud)

#### Virtual Platform Challenges

- Insufficient performance

- High complexity

- Limited vendor interoperability

- Limiting factors

- Modern simulation infrastructure

- Efficient standardization

- Fast models (especially CPU)

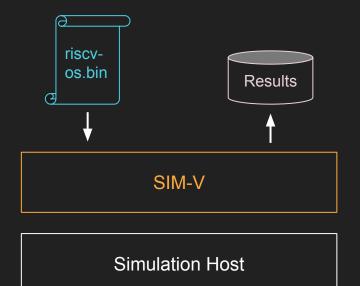

#### MachineWare SIM-V

- Fast, functional RISC-V simulator

- 2.5x faster than state-of-the-art

- Shift-left: Better software earlier

- Easy to use and integrate

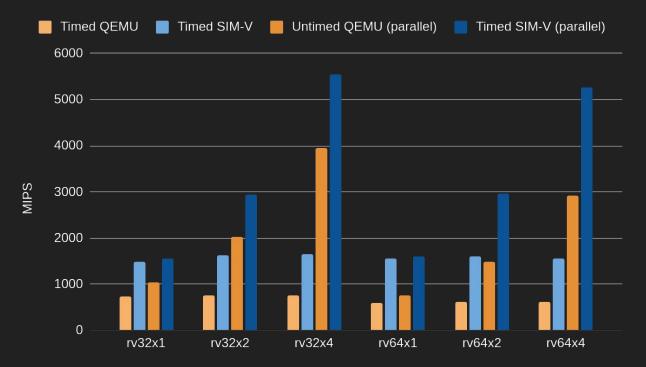

#### SIM-V vs. QEMU: Dhrystone

Number of Cores

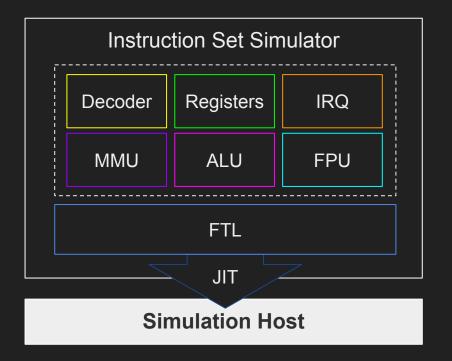

#### FTL - Fast Translator Library

Processor Modeling and High-Speed Dynamic Binary Translation Toolkit

- Model your processor in C++

- Fast JIT binary translation

- No target software limitations

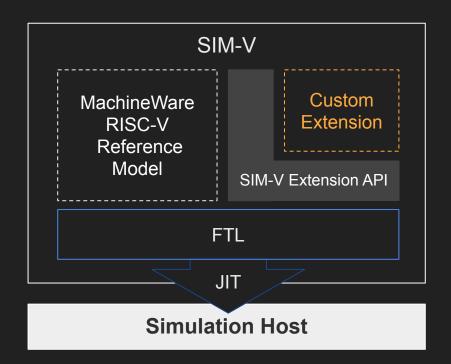

#### SIM-V Custom Extensions

- Add instructions, registers, ...

- **SDK** for extension development

- Automatically loaded by SIM-V

- Leverage FTL for performance

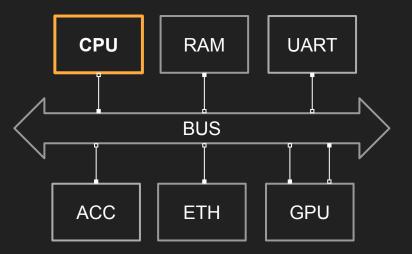

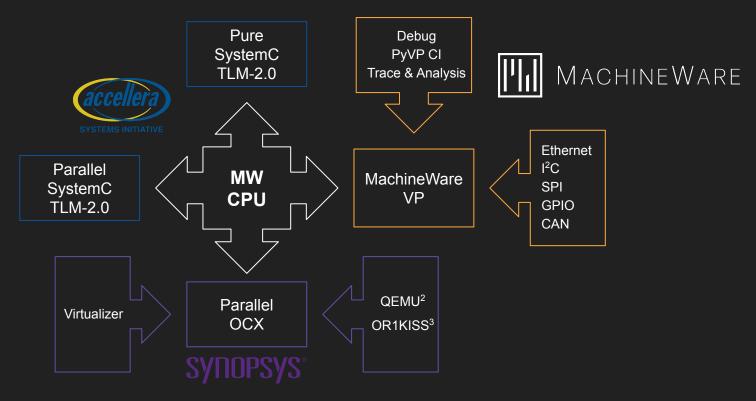

#### Interoperability

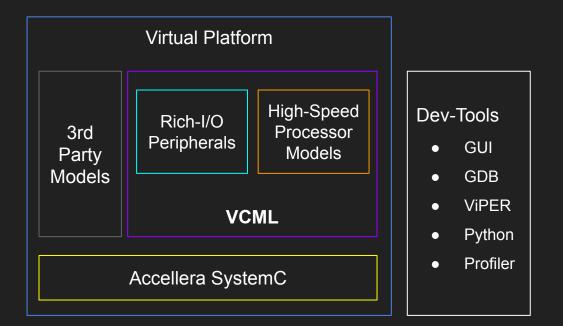

VCML - Virtual Components Modeling Library Rapid Virtual Platform construction and universal tool integration

- Open-source license

- Component models

- Tool integrations

- TLM protocols

- Modeling primitives

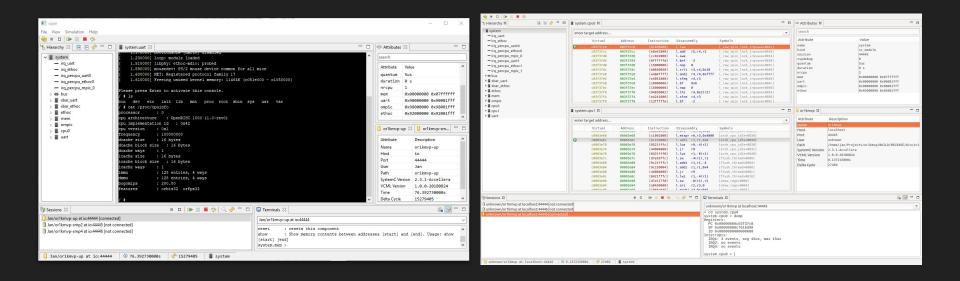

#### MachineWare Virtual Platform ExploreR (ViPER)

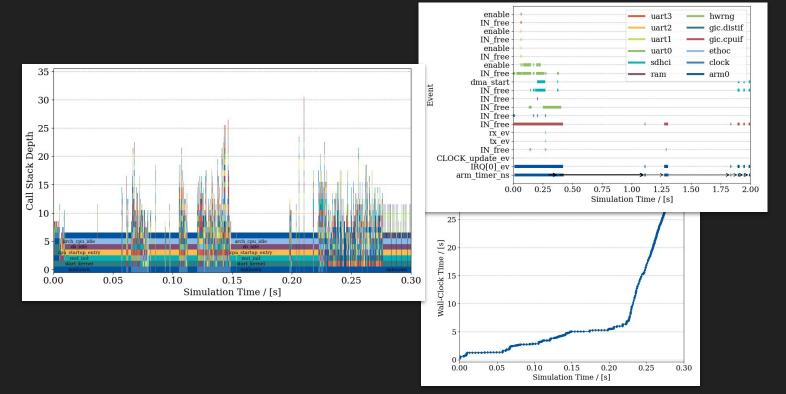

#### ViPER Trace and Analysis

- Python scripting for CI and test

- Connect to VP over network

- Control, configure, inspect VP

- Easy integration with Jenkins, Gitlab CI, ...

#### import pyvp

```

with pyvp.connect(localhost, 1234) as vp:

symbols = vp.cpu.get_symbols()

bp = symbols.search("start_kernel")

vp.cpu.set_breakpoint(bp)

vp.run(60)

if (vp.state() = pyvp.BREAKPOINT_HIT and

vp.cpu.get_pc() = bp.address):

print("TEST PASS")

else

print("TEST FAIL")

```

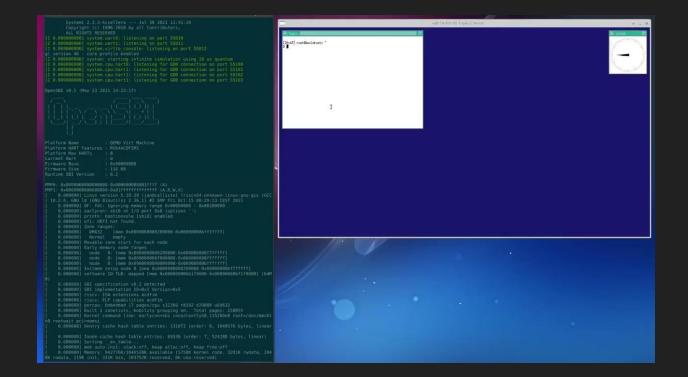

#### Demo

#### SIM-V Use Cases

- Early software development and test

- Utilize in VP or stand-alone to target bare-metal, hypervisor, OS, or user-space

- Reference model for comparison

- Execute in lock-step and compare states

- Target software analysis

- Code coverage, hot spot analysis, ...

- Continuous Integration

- Automate tests with SIM-V in Jenkins, Gitlab, ...

- Scale easily on-premise or in the cloud

SIM-V is an ultra-fast RISC-V Simulator (2x faster than Qemu) MachineWare FTL JIT engine for customizable processor modeling MachineWare VCML SystemC-TLM 2.0 modeling infrastructure

Reach out:

E-Mail: contact@mwa.re

www.machineware.de